### **cryptodev** Overview, status & future work

Declan Doherty DPDK Summit Userspace – Dublin, Oct 2016

### cryptodev

### **Overview**

#### Overview

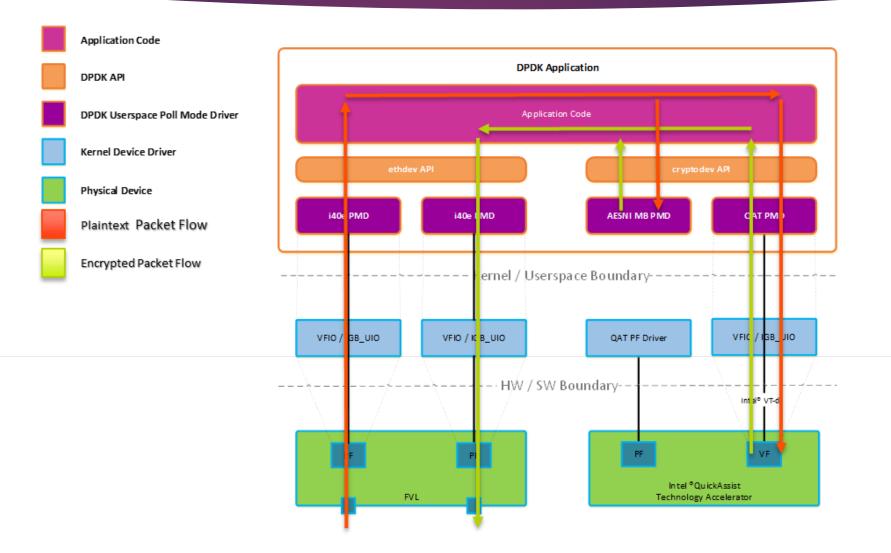

- Framework for processing symmetric crypto workloads in DPDK.

- Defines a standard API which supports both hardware accelerated lookaside and software based crypto processing.

- Underlying method of crypto operation processing is transparent to user application, allowing migration of work from hardware to software dynamically.

- Poll mode driver infrastructure for crypto devices.

- Supports cipher, authentication and AEAD symmetric crypto operations.

- Supports provisioning of chained cipher / authentication operations.

- Provide session management APIs

- Asynchronous burst processing API to amortise the cost of crypto operations across multiple packets and also to maximise performance when offloading to hardware accelerators.

### Crypto processing pipeline

### DPDK

### API Components

#### **DPDK CRYPTODEV API COMPONENTS** Device Symmetric Algorithms Symmetric Session Device Capabilities Definitions Management Management **Queue Pair Operation Processing** Device Operation Enqueue/Dequeue Management **Statistics Provisioning**

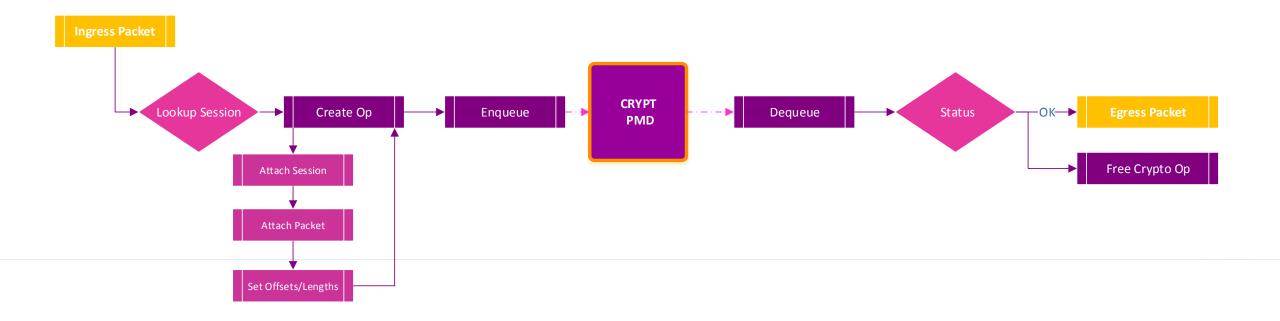

### Application Crypto Packet Processing Flow

### DPDK

### cryptodev

### Development

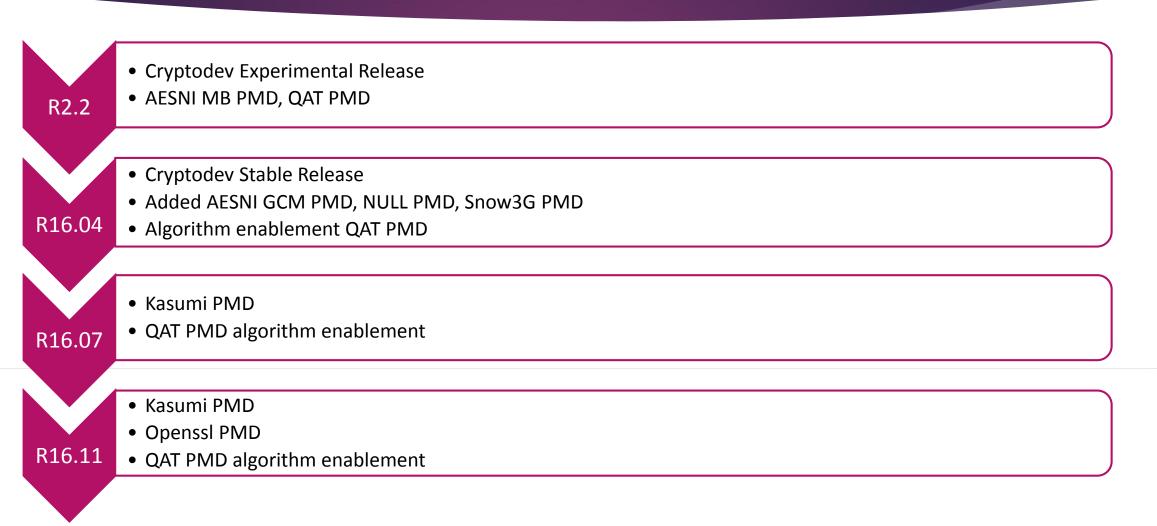

### Feature delivery since userspace '15

DPDK

### Changes from experimental release

# DPDK

#### Moved from a rte\_mbuf oriented

uint16\_t rte\_cryptodev\_enqueue\_burst (dev\_id, qp\_id, struct rte\_mbuf \*\*pkts, int16\_t nb\_pkts); uint16\_t rte\_cryptodev\_dequeue\_burst (dev\_id, qp\_id, struct rte\_mbuf \*\*pkts, int16\_t nb\_pkts);

#### to rte\_crypto\_op burst API

uint16\_t rte\_cryptodev\_enqueue\_burst (dev\_id, qp\_id, struct rte\_crypto\_op \*\*ops, int16\_t nb\_ops); uint16\_t rte\_cryptodev\_dequeue\_burst (dev\_id, qp\_id, struct rte\_crypto\_op \*\*ops, int16\_t nb\_ops);

- Simplified mbuf management, no need for extra metadata on mbuf. No requirement to check if crypto\_op needs to be freed on freeing of mbuf.

- Also stopped elements of cryptodev code being introduced into other parts of DPDK library code.

### Crypto Poll Mode Drivers

- crypto\_aesni\_gcm AESNI / vectorised accelerated software PMD

- crypto\_aesni\_mb AESNI / vectorised accelerated software PMD

- crypto\_kasumi Vectorised accelerated software PMD

- crypto\_openssl PMD which shims crypto operations into the Openssl's libcrypto

- crypto\_null software PMD

- crypto\_qat Intel<sup>®</sup> QuickAssist Technology hardware accelerator

- crypto\_snow3g Vectorised accelerated software PMD

- crypto\_zuc Vectorised accelerated software PMD

### Supported Algorithms

# DPDK

| Algorithm        | QAT*         | SW VECTORIZED | SW LEGACY    | Algorithm        | QAT*         | SW VECTORIZED | SW LEGACY    |

|------------------|--------------|---------------|--------------|------------------|--------------|---------------|--------------|

| AES GMAC 128-bit | ✓            |               | $\checkmark$ | 3DES CBC 128-bit | ✓            |               | ✓            |

| AES GMAC 192-bit | $\checkmark$ |               | $\checkmark$ | 3DES CBC 192-bit | ✓            |               | $\checkmark$ |

| AES GMAC 256-bit | $\checkmark$ |               | ✓            | 3DES CTR 128-bit |              |               | ✓            |

| AES XCBC 128-bit | $\checkmark$ | $\checkmark$  |              | 3DES CTR 192-bit |              | $\checkmark$  | $\checkmark$ |

| KASUMI F9        |              | $\checkmark$  |              | AES CBC 128-bit  | ✓            | ✓             | ✓            |

| MD5              |              |               | $\checkmark$ | AES CBC 192-bit  | $\checkmark$ | $\checkmark$  | $\checkmark$ |

| MD5_HMAC         | $\checkmark$ | $\checkmark$  | $\checkmark$ | AES CBC 256-bit  | ✓            | $\checkmark$  | ✓            |

| SHA1             |              |               | $\checkmark$ | AES CTR 128-bit  | $\checkmark$ | $\checkmark$  | $\checkmark$ |

| SHA1_HMAC        | $\checkmark$ | ✓             | $\checkmark$ | AES CTR 192-bit  | ✓            | $\checkmark$  | ✓            |

| SHA224           |              |               | $\checkmark$ | AES CTR 256-bit  | $\checkmark$ | $\checkmark$  | $\checkmark$ |

| SHA224_HMAC      | $\checkmark$ | ✓             | $\checkmark$ | KASUMI F8        |              | $\checkmark$  |              |

| SHA256           |              |               | $\checkmark$ | NULL             | $\checkmark$ | $\checkmark$  | $\checkmark$ |

| SHA256_HMAC      | $\checkmark$ | $\checkmark$  | $\checkmark$ | SNOW3G UEA2      | ✓            | $\checkmark$  |              |

| SHA384           |              |               | $\checkmark$ | ZUC EEA3         |              | $\checkmark$  |              |

| SHA384_HMAC      | $\checkmark$ | $\checkmark$  | ✓            |                  |              |               |              |

| SHA512           |              |               | $\checkmark$ | Algorithm        | QAT          | SW VECTORIZED | SW LEGACY    |

| SHA512_HMAC      | ✓            | ✓             | ✓            | AES GCM 128-bit  | ✓            | ✓             |              |

| SNOW3G UIA2      | ✓            | $\checkmark$  |              | AES GCM 192-bit  | $\checkmark$ |               |              |

| ZUC EEA3         |              | $\checkmark$  |              | AES GCM 256-bit  | $\checkmark$ |               |              |

\* QAT = Intel(R) QuickAssist Technology

### cryptodev

### Future Work

#### Framework / PMDs

- Adding rte\_mbuf scatter-gather support to all software crypto PMDs

- Migration of crypto\_aesni\_gcm to ISA-L crypto, enabling AES-GCM 256bit

- Cipher only/ authentication only operations to crypto\_aesni\_mb

- PCI Hot-plug support to framework

- Crypto operation performance optimisations

### **Crypto Performance Application**

- New application to enable benchmarking of crypto PMD performance on any system.

- Modular to allow any crypto PMD to be tested if it can support the algorithm combination.

- Allows configuration of all components of the PMD and all configuration of elements of the crypto operations to be executed.

- Will support throughput and latency measurement initially.

./crypto-perf \$eal\_options -- --ptest throughput --devtype crypto\_aesni\_gcm --optype aead --cipher-algo aes-gcm -cipher-op encrypt --cipher-key-sz 16 --auth-algo aes-gcm --auth-op generate --auth-key-sz 16 --auth-aad-sz 12 -auth-digest-sz 16 --total-ops 10000000 --silent --burst-sz 32 --buffer-sz 2048

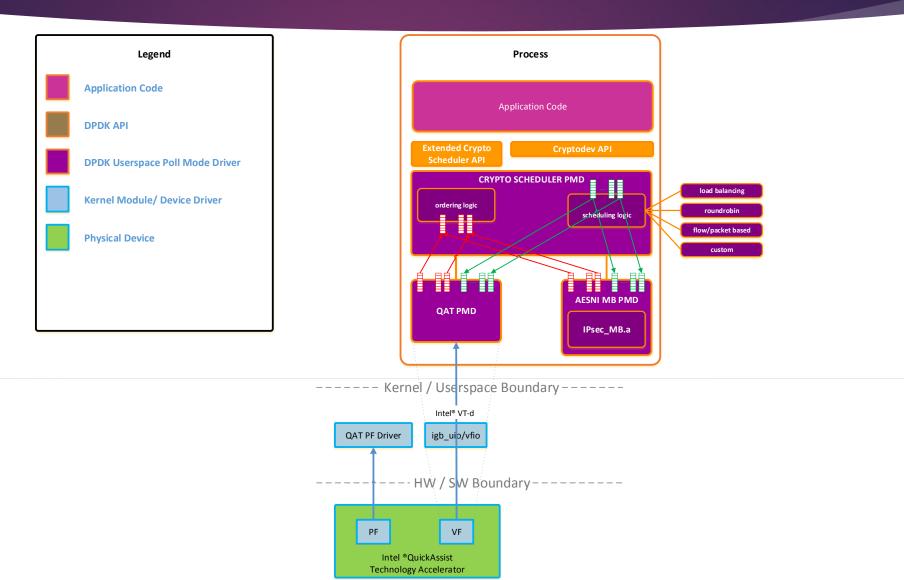

### Crypto Scheduler

- Allows multiple crypto devices to be slaved under a single device.

- Investigating per queue, per flow and per packet scheduling paradigms.

- Pluggable scheduling/ordering logic, may allow user to define there own scheduler and dynamically load.

- Many scheduling modes being investigated:

- ▶ fat flow load balancing a single flow across multiple hardware accelerators

- ▶ sw fallback allow flows to processed on core when hw accelerator is oversubscribed.

- per packet scheduling packet size / session type and PMD utilization used to decide crypto PMD to use.

- distributor balance across many cores for sw crypto

#### Crypto Scheduler PMD

### DPDK

### Questions?

Declan Doherty declan.doherty@intel.com

# Enabling IPSec Cryptodev Offload

Sergio González Monroy Network Software Engineer @ Intel DPDK Summit Userspace - Dublin- 2016

### IPSec Development

- Enabling Cryptodev in FD.IO/VPP

- Preliminary Performance

### Future Work

### Questions

#### **IPSec Development**

### DPDK

### **DPDK 16.04**

- IPSec-secgw sample app

- Basic data path functionality

- AES-CBC

- HMAC-SHA1-96

- ESP tunnel

### **DPDK 16.07**

- Transport Mode

- IPv6 support

### **DPDK 16.11**

- AES-GCM

- AES-CTR

- Config file

### VPP 16.06

- OpenSSL libcrypto

- IKEv2 (responder only)

- Anti-Replay Window

- Extended Sequence Number (ESN)

- Nested SAs

- IPSec interface (VPN)

### VPP 16.09

• L2GRE over IPSec

### VPP 17.01

- Enable Cryptodev

- AES-GCM

- Dynamic Anti-Replay Window

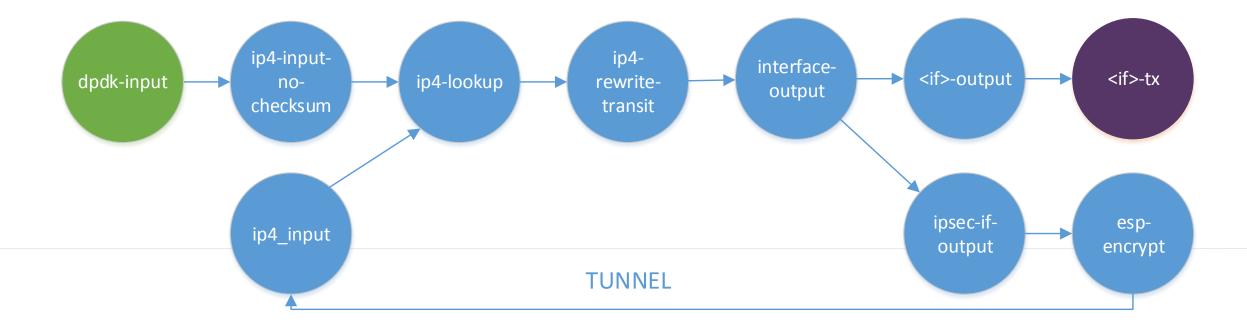

### Enabling Cryptodev in FD.IO/VPP (1)

# DPDK

VPP IPSec interface graph – outbound path

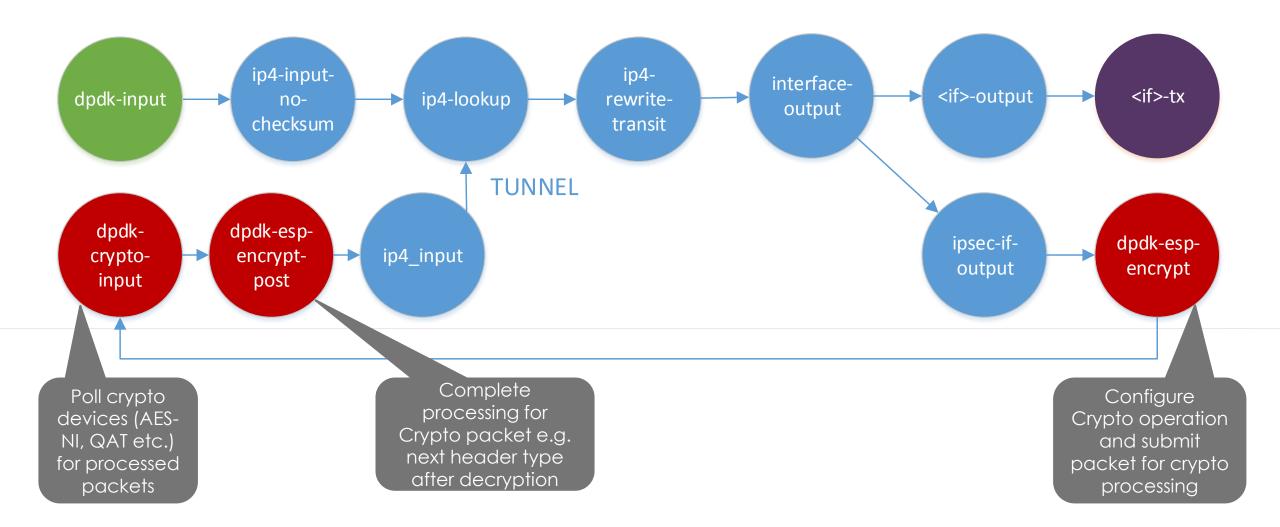

### Enabling Cryptodev in FD.IO/VPP (2)

## DPDK

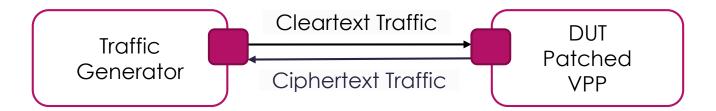

### Test Setup

### DPDK

- Intel<sup>®</sup> Xeon<sup>®</sup> DP-based Server (2 CPU sockets).

- Intel(R) Xeon(R) CPU E5-2699 v3 @ 2.30GHz (Haswell)

- 18 physical cores per CPU (i.e. per socket)

- 128 GB DDR4 RDIMM Crucial Server capacity = 64 GB RAM (16 x 8 GB). Tested with 128 G

- 1 x Intel<sup>®</sup> 82599 10 Gigabit Ethernet Controller

- 1 x Intel Corporation DH895XCC Series

Intel<sup>®</sup> QuickAssist Technology (Coletto Creek)

- Operating System: Ubuntu 16.04, Kernel version: 4.4.0-22-generic

- VPP commit ID: 154d445f7f8f1553d9bb00d1be42bf1b06eda9f1

- Intel(R) DPDK 16.04

- Single data processing core

- All hardware local to socket

| BIOS Settings                                                 | Setting                  |

|---------------------------------------------------------------|--------------------------|

| Enhanced Intel SpeedStep®                                     | DISABLED                 |

| Processor C3                                                  | DISABLED                 |

| Processor C6                                                  | DISABLED                 |

| Intel® Hyper-Threading Technology (HTT)                       | DISABLED                 |

| Intel® Virtualization Technology                              | ENABLED                  |

| Intel® Virtualization Technology for Directed I/O (VT-d)      | DISABLED                 |

| MLC Streamer                                                  | ENABLED                  |

| MLC Spatial Prefetcher                                        | ENABLED                  |

| DCU Data Prefetcher                                           | ENABLED                  |

| DCU Instruction Prefetcher                                    | ENABLED                  |

| Direct Cache Access (DCA)                                     | ENABLED                  |

| CPU Power and Performance Policy                              | Performance              |

| Memory Power Optimization                                     | Performance<br>Optimized |

| Intel® Turbo boost                                            | OFF                      |

| Memory RAS and Performance Configuration -> NUMA<br>Optimized | ENABLED                  |

Results will vary depending on software, workloads and system configuration

### VPP Configuration

# DPDK

set int ip address TenGigabitEthernet86/0/0 192.168.10.1/24

set int promiscuous on TenGigabitEthernet86/0/1

set int ip address TenGigabitEthernet86/0/1 192.168.1.1/24

set int promiscuous on TenGigabitEthernet86/0/1

create ipsec tunnel local-ip 192.168.1.1 local-spi 1111 remote-ip 192.168.1.2 remote-spi 2222

set interface ipsec key ipsec0 local crypto aes-cbc-128 2b7e151628aed2a6abf7158809cf4f3d set interface ipsec key ipsec0 local integ sha1-96 6867666568676665686766656867666568676665 set interface ipsec key ipsec0 remote crypto aes-cbc-128 2b7e151628aed2a6abf7158809cf4f3d set interface ipsec key ipsec0 remote integ sha1-96 686766656867666568676665686766656867666568676665

ip route add 192.168.20.2/32 via ipsec0

set ip arp TenGigabitEthernet86/0/0 192.168.1.2 90:e2:ba:b0:dc:69

set int state TenGigabitEthernet86/0/1 up

set int state TenGigabitEthernet86/0/0 up

set int state ipsec0 up

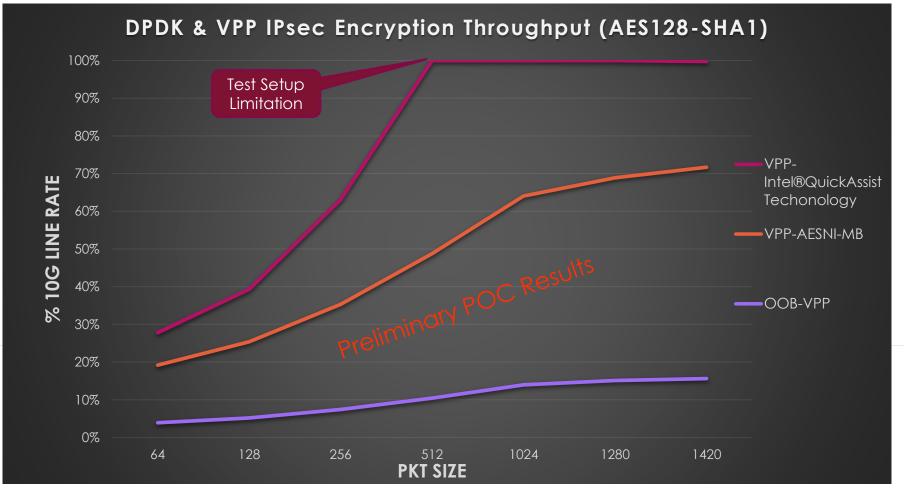

### Early Development Performance

Results have been estimated or simulated using internal Intel analysis or architecture simulation or modeling, and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

### Future Work

- Cryptodev Load-Balancer/Scheduler

- Crypto PMDs improvements

- Support for more crypto algorithms

- Scatter-Gather List Support

### Questions?

Sergio González Monroy sergio.gonzalez.monroy@intel.com

### Legal Disclaimers

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

© 2016 Intel Corporation. Intel, the Intel logo, Intel. Experience What's Inside, and the Intel. Experience What's Inside logo are trademarks of Intel. Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.